Low-power hyperspectral anomaly detector implementation in cost-optimized FPGA devices

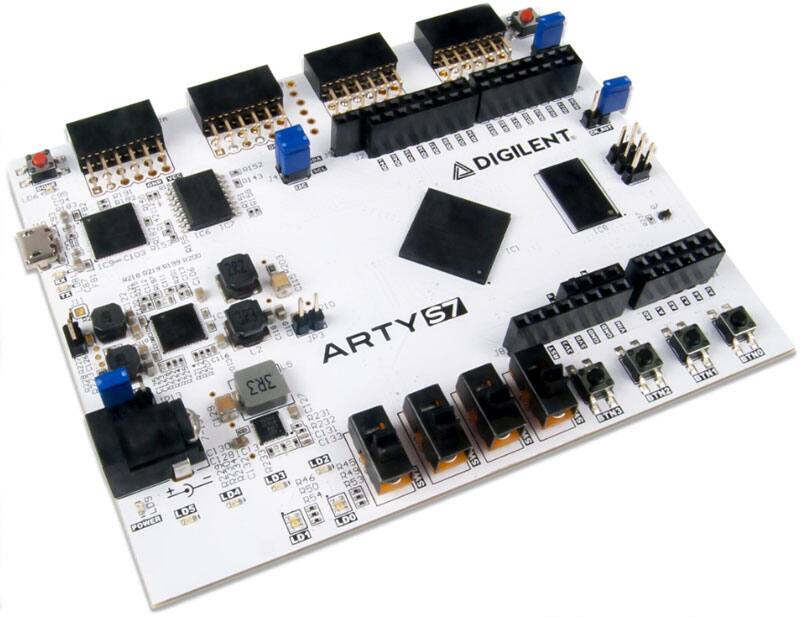

Onboard data processing for on-the-fly decision-making applications has recently gained momentum in the field of remote sensing. In this context, hyperspectral anomaly detection has received a special attention since its main purpose lays on the identification of abnormal events in an unsupervised manner. Nevertheless, onboard real-time hyperspectral image processing still poses several challenges before becoming a reality. This is why there is an emerging trend towards the development of hardware-friendly algorithmic solutions embedded in reconfigurable devices. In this context, this work contributes with a hardware architecture that ensures a progressive line processing in time-sensitive applications limited by the scarcity of hardware resources. In this sense, we have implemented the state-of-the-art HW-LbL-FAD detector on a reconfigurable hardware for a real-time performance. Specifically, we have selected a cost-optimized FPGA (ZC7Z020-CLG484) to implement our solution whose results draw up a good trade-off between the following three features: time performance, energy consumption and cost. The experimental results indicate our hardware component is able to process hyperspectral images of 825×1024 pixels and 160 bands in 0.51 seconds with a power-budget of 1.3 watts and a device cost around 150 C. Regarding detection performance, the HW-LbL-FAD algorithm outperforms other state-of-the-art algorithms.

Publicado por miembros del grupo Arco

👀📜

— Arco Research – UCLM (@ARCOresearch) March 15, 2022

◾You can now have a look at our article «Low-power hyperspectral anomaly detector implementation in cost-optimised FPGA devices», made in collaboration with #IUMA of the @ULPGC for the #IEEEJSTARS magazine.#HyperspectralImaging #AnomalyDetection https://t.co/RSKwprrB8U